DigiTimes 8 月 29 日发布博文,表示在英伟达的不断催促下,台积电不仅开足马力进军半导体扇出面板级封装(FOPLP),而且大力投资玻璃基板研发工艺,以期实现突破。

IT之家援引消息源报道,台积电将会在 9 月召开的半导体会议上,公布 FOPLP 封装技术细节,并公开玻璃基板尺寸规格。

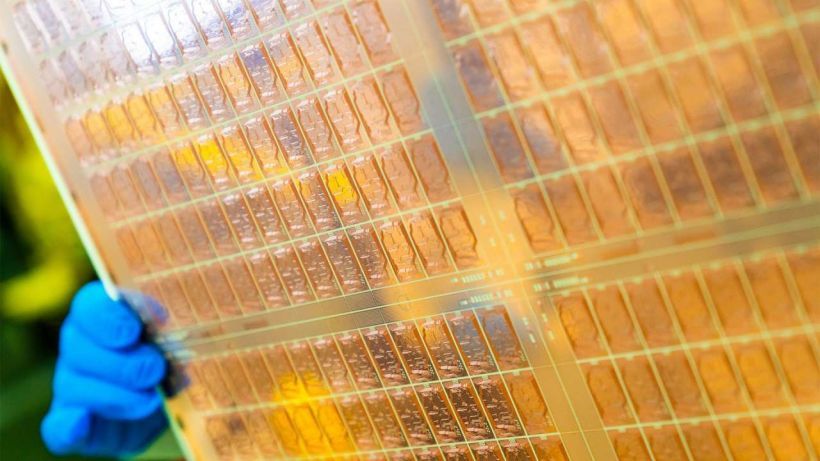

玻璃基板制程涵盖玻璃金属化(Glass Metallization)、后续的 ABF 压合制程,以及最终的玻璃基板切割。

在玻璃金属化完成后的玻璃又称做“Glass Core”,制程涉及 TGV(Through-Glass Via)、湿蚀刻(Wet Etching)、AOI 光学检测、镀膜(Sputtering)及电镀(Plating)。

玻璃基板的尺寸为 515×510mm,在半导体和载板制程中均属于全新制程,其关键在于第一道工序“TGV”。

尽管这项技术早在 10 年前就已问世,但其速度未能满足量产需求,仅能达到每秒 10~50 个孔,使得玻璃基板技术至今尚未能起飞。

目前仅英特尔宣称具备量产能力,尚未有其他厂商能提供完整且成熟的制程设备或服务,但业界则盛传台积电已重启研发。

关于玻璃基板何时投放市场,之前的一篇报道披露,主要制造商都把解决方案投放市场的时间窗口定在了 2025-2026 年,其中英特尔和台积电走在了前列。